### **AND8429/D**

Former Catalyst Document Number MD-6000

### Using ON Semiconductor's Serial EEPROMs in Shared Input/Output Configuration

ON Semiconductor®

http://onsemi.com

### Prepared by:

ON Semiconductor

ON Semiconductor's family of serial E<sup>2</sup>PROMs utilizes 4 signals for the communication interface; Chip Select (CS) for device selection, Serial Clock (SK or CLK) for synchronizing serial data to and from the device, Data Input (DI) to input serial data to the device and Data Output (DO) to output serial data from the device. This interface can be reduced to 3 signals by sharing DI and DO as a common input/output signal. However, the following precautions should be taken to prevent problems due to DI/DO contention:

# 1) READ Instruction in Shared DI/DO Configuration: (applies to 93C46, 93C56, 93C57, 93C66 and 93C86)

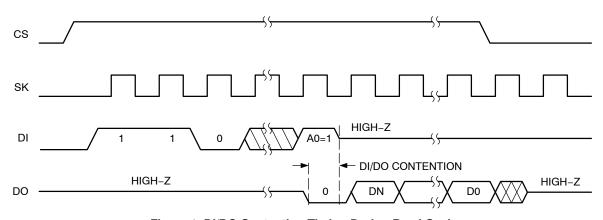

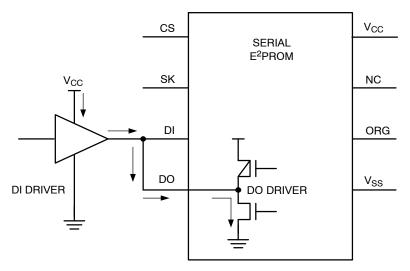

Data Output Pin (DO) remains in high impedance state while most of the READ instruction (i.e. start bit, opcode and address) is being input and offers no contention to the Data Input Pin (DI) driver in a shared DI/DO configuration (Figure 1). However, typically 50 ns after the rising edge of the serial clock shifts in the least significant bit of the address stream (A0), DO outputs the dummy '0' bit to flag the beginning of the output data stream. If A0 is a '1' and the DI driver has not been disabled by the time the '0' dummy bit becomes valid, a low impedance path between the system power supply and ground is created through the DI driver pullup and DO pulldown device (Figure 2).

#### **APPLICATION NOTE**

Unless this condition causes excessive noise on the system power supply (which may in turn cause noisy or spurious signals to the device), the READ instruction will continue and complete normally since A0 is already shifted into the device.

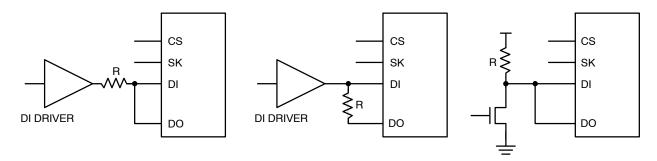

To minimize potential problems during this low impedance condition, a current limiting resistor should be placed between the DI driver and the DO pin when in shared DI/DO configuration (Figure 3).

Alternatively, an open drain (or open collector) DI driver with pullup resistor could be used (Figure 3).

In either case, the clocking rate should be slow enough to ensure that the resistor can charge or discharge the shared DI/DO bus capacitance before the appropriate clock edge. For example, if the resistor used is 10 K $\Omega$ , and the bus capacitance is 100 pF, then a safe clock rate is calculated to be:

Clock Period (T) =  $2 \times 3RC$ =  $2 \times 3 \times 10 \times 100 \text{ pF}$ =  $6 \text{ } \mu\text{sec}$ Frequency (f) = 1 / T= 167 KHz

Figure 1. DI/DO Contention Timing During Read Cycle

#### AND8429/D

Figure 2. Current Path

Figure 3. Possible Configurations to Minimize Problems Due to READ Contention

# 2) Programming Instructions in Shared DI/DO Configuration:

(93C46, 93C56, 93C57, 93C66 and 93C86 only)

All 3-Wire devices feature self-timed programming cycles. A programming status signal indicates whether the self-timed programming cycle is still in progress or has been completed. A '0' status signal indicates that the device is still programming mode, while a '1' status signal indicates that the programming cycle has been completed and the device is ready to receive the next instruction. This feature will allow a user to minimize the programming time (t<sub>EW</sub>).

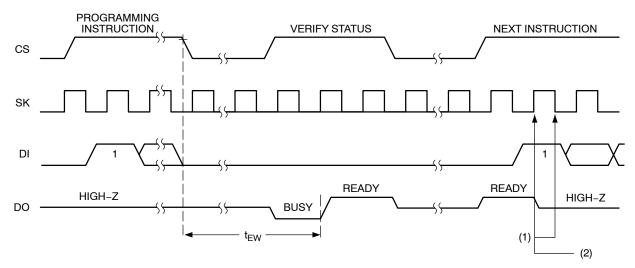

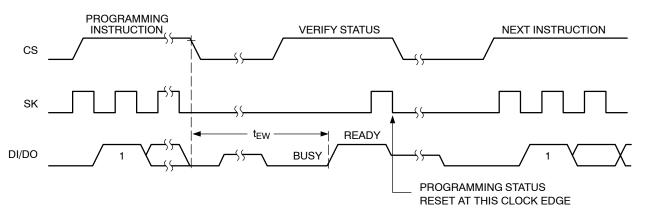

On the 93C46, 93C56, 93C57, 93C66 and 93C86 serial E<sup>2</sup>PROMs, the programming status signal can be read on the DO pin by bringing CS high after initiating a programming cycle. In a 4–signal interface, after a programming cycle is complete, the status signal is reset to high impedance by the start bit of the next instruction (Figure 4).

In a shared DI/DO configuration, the '1' status signal on DO can be clocked into the device as a start bit and reset the status signal before it can be read. This can interfere with the DI signal of the next instruction cycle. The following steps are recommended to avoid these conditions for a 3-signal interface (Figure 5):

- 1. The clock (SK) should be stopped after shifting in the programming instruction. This prevents the '1' ready status from resetting the status signal before it can be read.

- 2. After reading the '1' ready status, at least one clock pulse should be input to the device while the DI/DO signal is '1' in order to reset the status signal.

- 3. CS should then be brought low to reset the instruction logic.

The next instruction can now be executed without any contention from the DO signal.

#### AND8429/D

Figure 4. Programming Instruction and Status Reset with 4-Signal Interface

Figure 5. Programming Instruction and Status Reset with 3-Signal Interface

- 1. Programming status reset on falling clock edge (93C46).

- 2. Programming status reset on rising clock edge (93C46, 93C57, 93C66 and 93C86).

ON Semiconductor and were registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative